最新記事公開時にプッシュ通知します

“アナログコンピュータ”でGPU超え? 特定の演算でH100の10倍高速かつ省エネ、AI学習へも応用可能性、Nature系列誌で発表

2025年10月31日

先端テクノロジーの研究を論文ベースで記事にするWebメディア「Seamless/シームレス」を運営。最新の研究情報をX(@shiropen2)にて更新中。

中国の北京大学などに所属する研究者らがNature Electronicsで発表した論文「Precise and scalable analogue matrix equation solving using resistive random-access memory chips」は、従来のデジタルコンピュータが抱える計算速度とエネルギー効率の限界を突破し得るアナログコンピューティングを用いた行列演算の精度問題を解決する新方式を提案した研究報告である。

抵抗変化型メモリを用いて

日常的に使うノートパソコンやスマートフォンなどは、データを0か1の2進数として処理するデジタルコンピュータである。一方、アナログコンピュータで用いられるアナログコンピューティングでは、電気抵抗などの連続的に変化する物理量を直接利用してデータを処理する。アナログ方式は原理的に高速かつ省エネルギーだが、物理デバイスの誤差や温度変化、ノイズの影響により、これまでデジタル方式ほどの精度を実現できなかった。

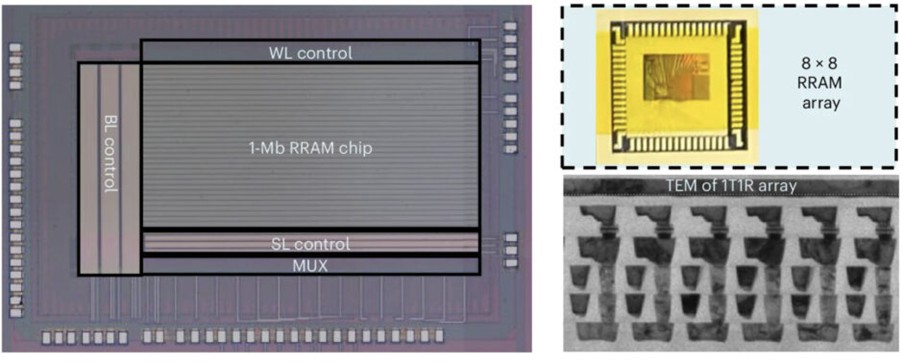

研究チームはこの課題に対し、「RRAM」(Resistive Random-Access Memory)を用いた新しいアプローチを実証した。RRAMは、電圧をかけて抵抗値を変化させることでデータを記憶する不揮発性メモリである。

新方式のポイントは、低精度だが高速演算できる「Low-Precision INV」(LP-INV)と高精度で行列とベクトルの積を行う「High-Precision MVM」(HP-MVM)を組み合わせた反復アルゴリズムにある。まずLP-INVで近似解を素早く求め、その誤差をHP-MVMで評価して修正する。この過程を数回繰り返すことで、段階的に精度を向上させる。

実験では、商用40nmCMOSプロセスで製造された、HP-MVM向け1メガビットRRAMチップと、LP-INV向け8×8個のRRAMアレイチップを使用し、16×16の実数値行列の逆行列を24ビット固定小数点精度で計算することに成功した。これは一般的なコンピュータが使用する32ビット浮動小数点演算とほぼ同等の精度である。

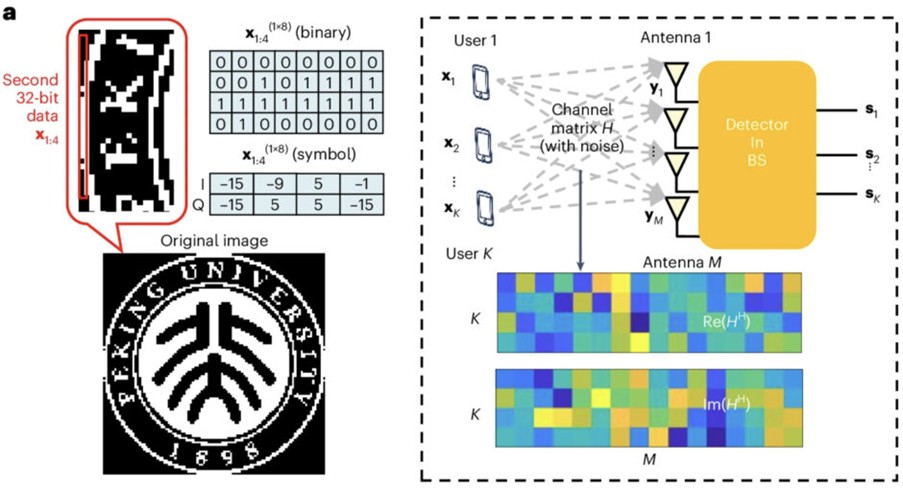

この技術の実用性を実証するため、研究チームは次世代無線通信(5G/6G)の基盤技術である大規模MIMO(Multiple-Input Multiple-Output)システムへの応用実験を行った。現代の無線通信では、基地局が多数のアンテナを使って複数の端末と同時通信する際、大規模な行列計算が必要となる。

実験では128本のアンテナを持つ基地局で8台の端末からの信号を同時処理し、32ビット浮動小数点デジタル処理と同等の性能を達成した。この成果は、アナログコンピューティングが5G/6G時代の大規模MIMO信号処理において実用的な解決策となる可能性を示している。

NVIDIA H100、AMD Vega 20など最新GPUと比較

性能評価では、NVIDIA のH100やAMDのVega 20などの最新GPUと同じ計算精度で比較を行った(単一コアに正規化して比較)。32×32サイズの行列計算でアナログ方式がデジタルプロセッサを上回り、128×128サイズでは約10倍のスループット向上と3〜5倍のエネルギー効率改善を実現した。

さらにBlockAMC(アナログ計算を大規模化するためのブロック分割手法)を使わない直接実装や、より高性能な演算増幅器を使用するなどのさらなる改良により、1000倍の処理速度向上と100倍近いエネルギー効率の改善が可能であるという。

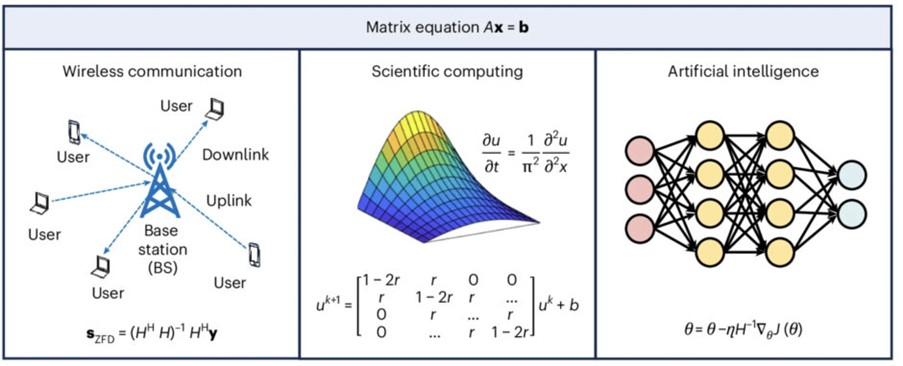

これらの研究結果は、アナログコンピューティングが現代の半導体技術と組み合さることで、デジタルコンピューティングの限界を突破する可能性を示した。特に無線通信におけるMIMO信号処理、科学計算における微分方程式の解法、人工知能におけるニューラルネットワークのトレーニングなどの大規模な行列演算が必要な分野での応用が期待される。

Source and Image Credits: Zuo, P., Wang, Q., Luo, Y. et al. Precise and scalable analogue matrix equation solving using resistive random-access memory chips. Nat Electron (2025). https://doi.org/10.1038/s41928-025-01477-0

関連記事

Googleの「量子超越性」覆す。NVIDIAの「A100」2300個超を使って量子コンピュータ凌駕【研究紹介】

光コンピュータでAI処理、GPUの295倍の計算速度を実現するプロセッサも? Nature誌に論文2本【研究紹介】

電力不要「“ゴム”コンピュータ」 伸縮により「0」と「1」をカウント【研究紹介】

人気記事